近日,我院系统结构研究室边缘性缺陷测试研究团队提出一种可用于6T SRAM(FinFET工艺)自热效应表征方法并在基于FinFET的高性能FPGA平台上进行了实验验证。相关成果以“Self-Heating Effect Analysis and Characterization of 6T SRAM Based on Delay Variation”为题发表在电子器件类著名期刊IEEE Transactions on Electron Devices (Doi: 10.1109/TED.2024.3465470)。

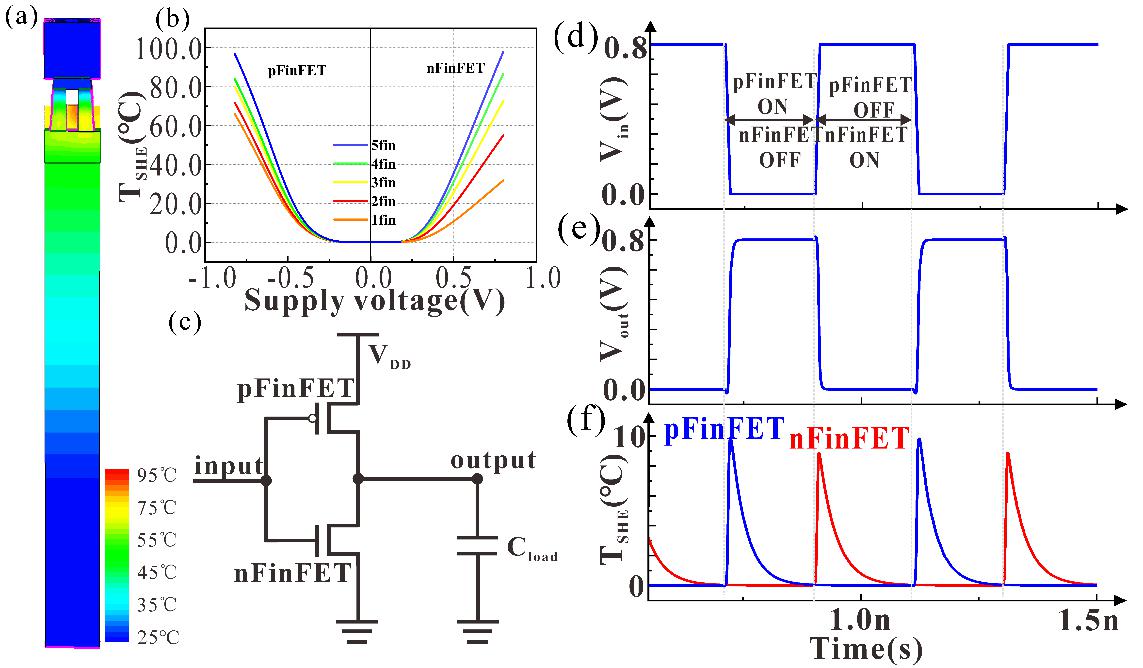

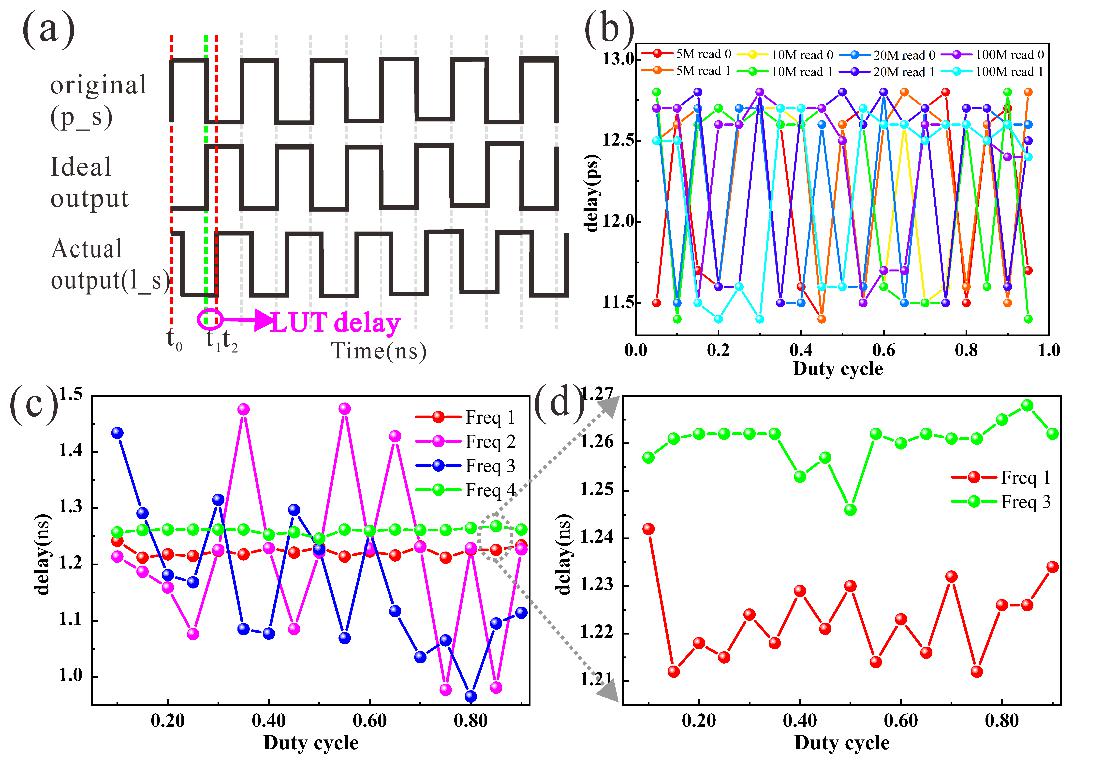

随着集成电路技术节点的不断发展,3D的晶体管结构和先进材料的使用增强了晶体管的自热效应,加速了缺陷产生,降低了驱动电流,增大了晶体管功耗,进而使得晶体管可靠性下降,严重的可至电路失效。因此,有效的针对基于先进纳米工艺的高集成密度SRAM的自热效应进行表征对电路的可靠性研究具有重要意义。该团队利用占空比和电路性能参数读延迟时间来实现6T SRAM的自热效应表征。

文章通过Hspice工具分别仿真了6T SRAM的保持、读和写三种状态,分析了自热效应对6T SRAM不同状态的影响。且进一步改变读状态下的占空比,提取读延迟参数随占空比的变化发现读延迟呈上升、不变和下降趋势。使用理论深入解析了产生该趋势的产生机理,并有效的利用读延迟变化进行自热效应表征。最后,在基于FinFET工艺的FPGA平台上进行了实验验证。研究结果表明,所提出的自热效应表征方法可用于瞬态温度:0-84.5℃,电路温度:0-48.8℃的表征温度范围。

该论文得到国家重大科研仪器研制项目及国家自然科学基金项目的资助。合肥工业大学为该论文唯一署名单位。作者包括汪月、梁华国教授、王斯禹、章宏、李丹青、鲁迎春副教授(通讯作者)、易茂祥教授、黄正峰教授。

论文链接地址:https://ieeexplore.ieee.org/stamp/stamp.jsp?tp=&arnumber=10722872&tag=1