- 5.1 概述

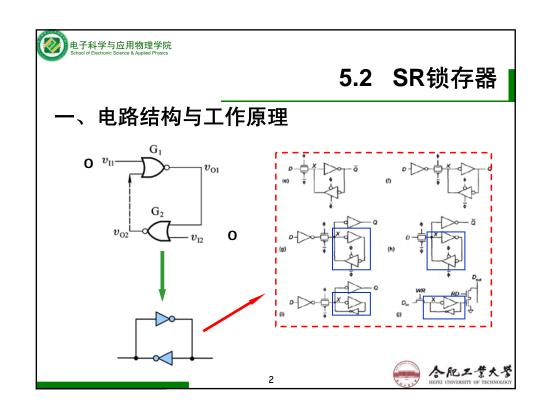

- 5.2 SR锁存器

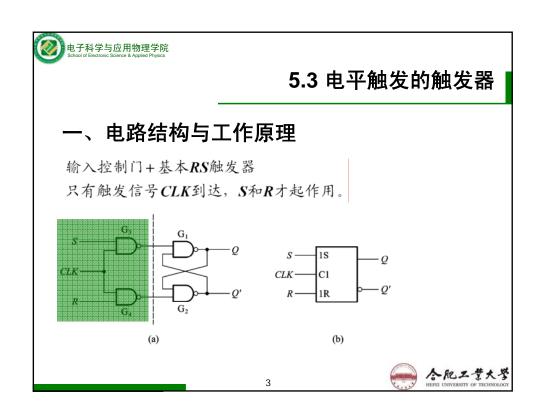

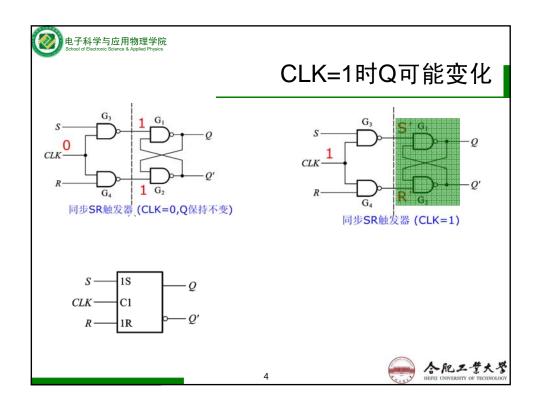

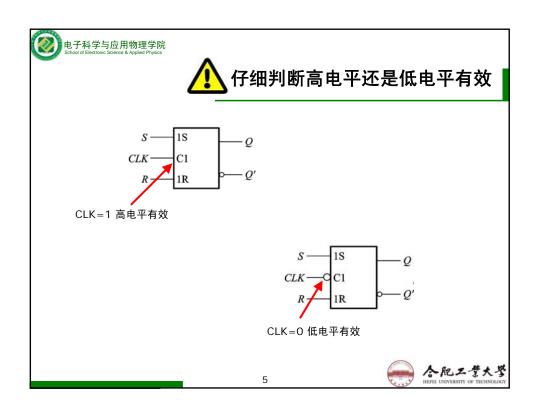

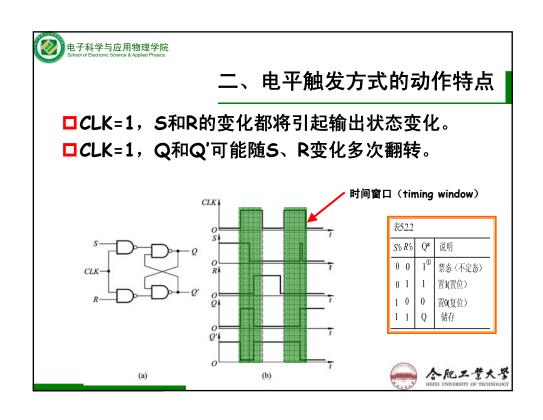

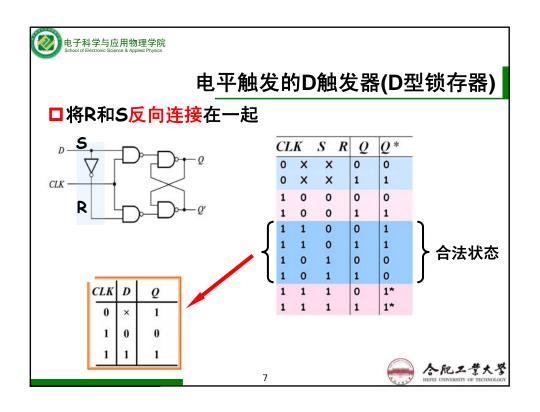

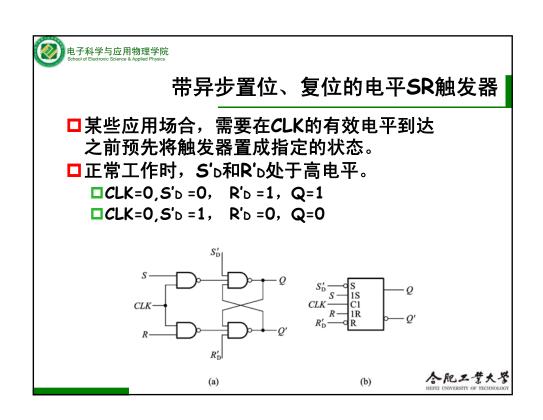

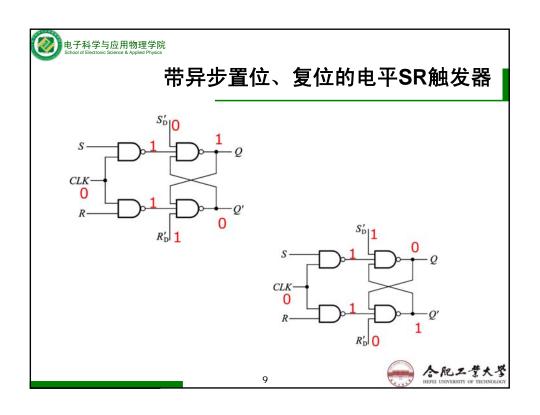

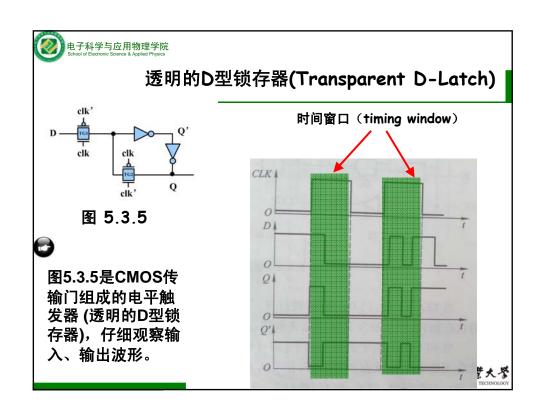

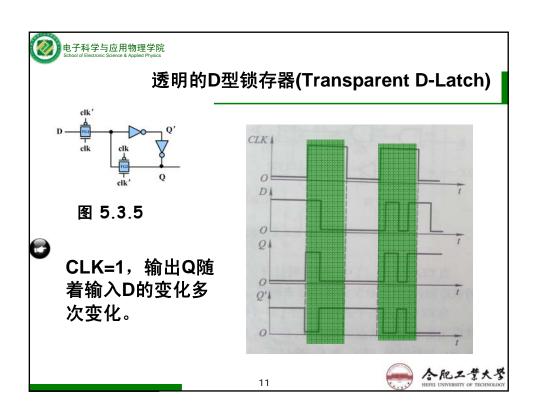

- 5.3 电平触发的触发器

- 5.4 脉冲触发的触发器

- 5.5 边沿触发的触发器

- 5.6 触发器的逻辑功能及其描述方法

- \*5.7 触发器的动态特性

#### 内容介绍

本章介绍构成时序逻辑电路的最基本部件一<mark>双稳</mark> <mark>态触发器</mark>,重点介绍各触发器的结构、工作原理、动 作特点,以及触发器从功能上的分类及相互间的转换。

首先从组成各类触发器的基本部分-SR锁存器入手,介绍触发器的结构、逻辑功能、动作特点,在基础上介绍JK触发器、D触发器、T触发器等,给出触发器的描述方程。

本章重点是各触发器的功能表、逻辑符号、触发电 平、状态方程的描述等。

#### 基本概念

#### 锁存器和触发器的区别?

- 1. 锁存器是Latch,触发器是flip-flop。

- 2. 不同的教科书中对latch和flip-flop的定义不同。

- 3. <u>阎石教材</u>中除了SR锁存器,都是触发器。

- 4. .....

## 5.1 概述

- 一、用于记忆1个比特位的二进制信号

- 1. 有两个能自行保持的状态

- 2. 根据输入信号可以置成O或1

#### 二、分类

- 1. 按触发方式(电平,脉冲,边沿)

- 2. 按逻辑功能 (RS, JK, D, T)

- 3. 按数据存储原理(静态触发器、动态触发器)

◆肥工堂大学 HEFEI UNIVERSITY OF TECHNOLOGY

- 5.1 概述

- 5.2 SR锁存器

- 5.3 电平触发的触发器

- 5.4 脉冲触发的触发器

- 5.5 边沿触发的触发器

- 5.6 触发器的逻辑功能及其描述方法

- \*5.7 触发器的动态特性

## 常用缩写

$\square G$ : Gate 表示门级单元

□R : Reset

**□**5 : **5**et

□时钟信号: CK CLK Clock

□Q的输出取反: Q' QF Q

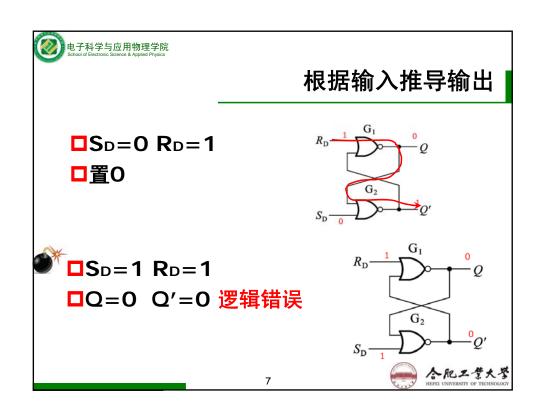

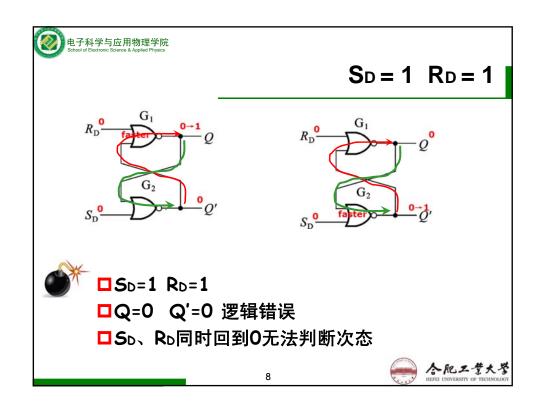

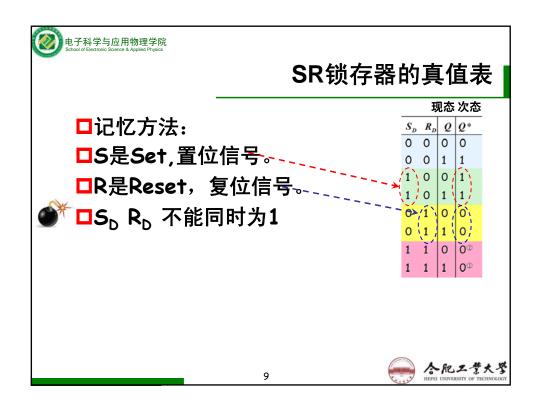

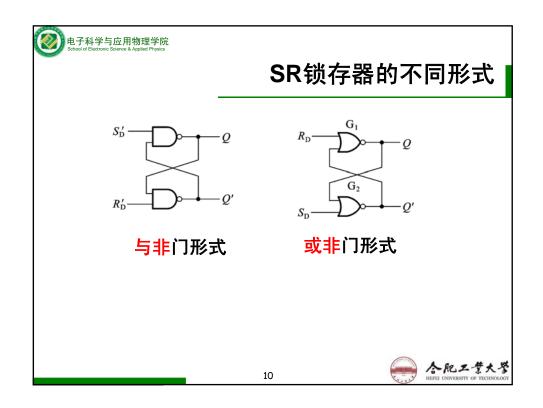

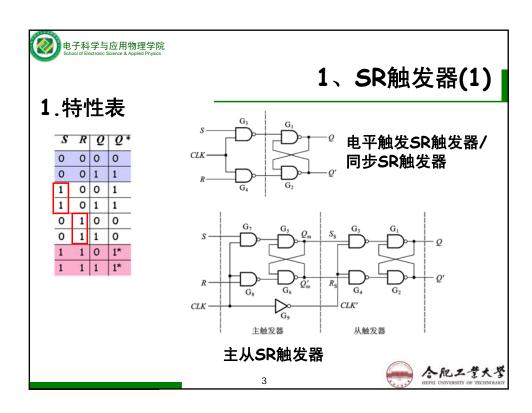

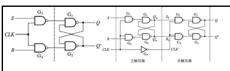

# SR锁存器的不同形式

与非门形式

或非门形式

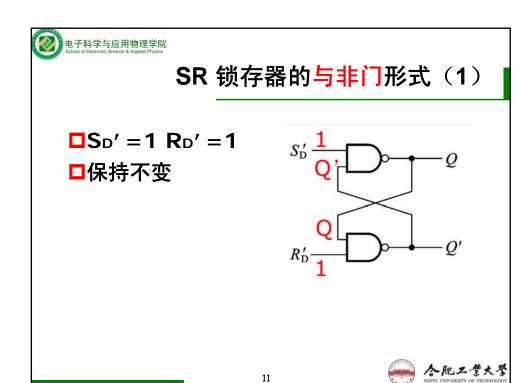

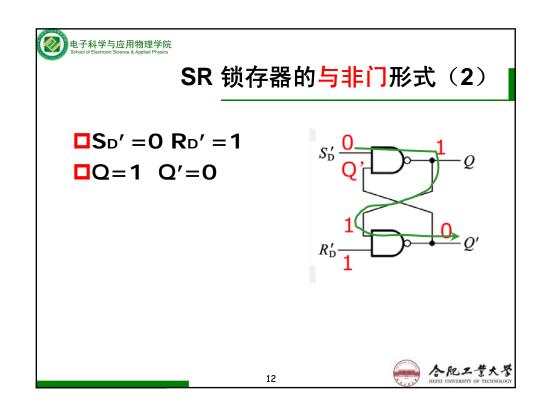

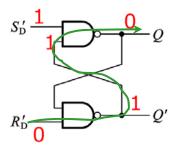

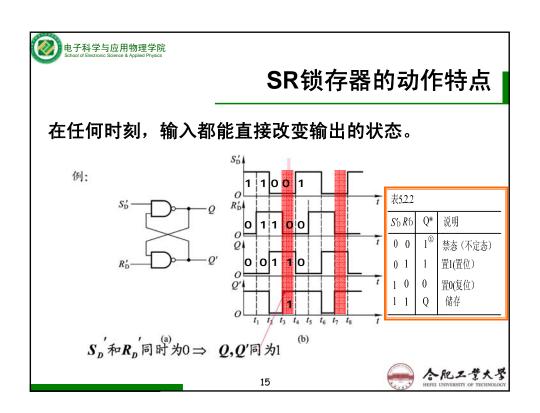

# SR 锁存器的与非门形式(3)

$\square$ SD' = 1 RD' = 0

□Q=0 Q'=1

13

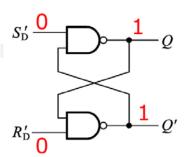

# SR 锁存器的与非门形式(4)

$\square S_{D'} = 0 R_{D'} = 0$

<sup>™</sup> □Q=1 Q'=1 非法状态

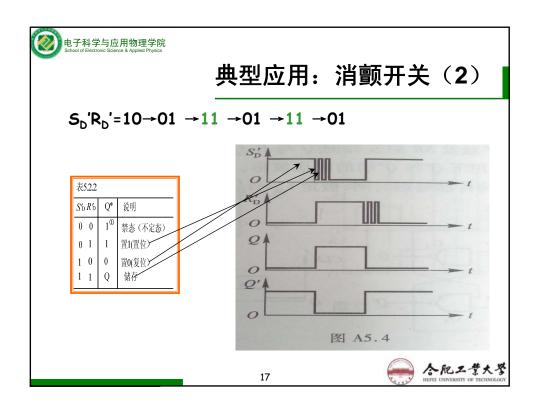

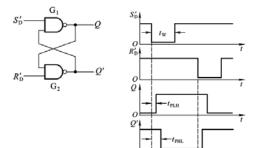

## 典型应用:消颤开关(1)

拨动开关S时,由于开关触点接通瞬间发生颤动,要求画出Q、Q'的波形。

$$S_D'R_D'=10\rightarrow 01\rightarrow 11\rightarrow 01\rightarrow 11\rightarrow 01$$

- 5.1 概述

- 5.2 SR锁存器

- 5.3 电平触发的触发器

- 5.4 脉冲触发的触发器

- 5.5 边沿触发的触发器

- 5.6 触发器的逻辑功能及其描述方法

- \*5.7 触发器的动态特性

电子科学与应用物理学院

#### 时钟触发器

- □ 在数字系统中,常常要求某些触发器在同一时刻动作,这就要求有一个同步信号来控制,这个控制信号叫做时钟信号(Clock),简称时钟,用CLK表示。这种受时钟控制的触发器统称为时钟触发器。

- □ 时钟的频率、相位、上升延迟、下降延迟对于电路工作特性具有重要影响。

- 5.1 概述

- 5.2 SR锁存器

- 5.3 电平触发的触发器

- 5.4 脉冲触发的触发器

- 5.5 边沿触发的触发器

- 5.6 触发器的逻辑功能及其描述方法

- \*5.7 触发器的动态特性

今肥工学大学 HEFEI UNIVERSITY OF TECHNOLOGY

电子科学与应用物理学院

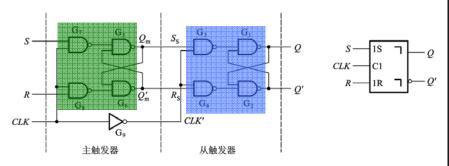

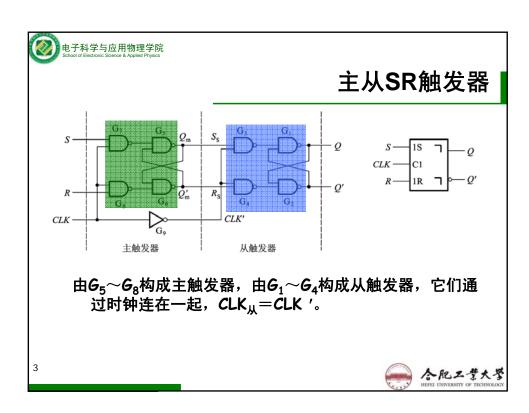

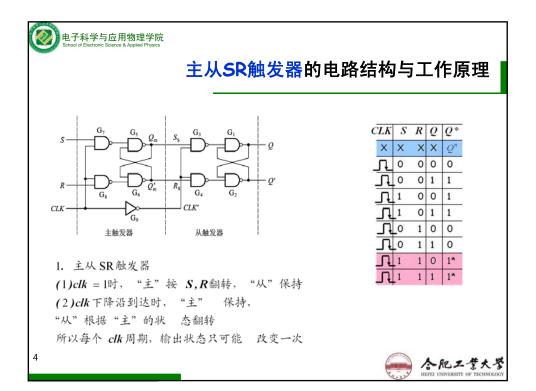

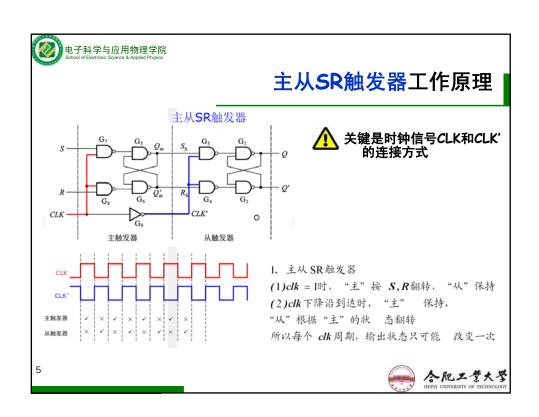

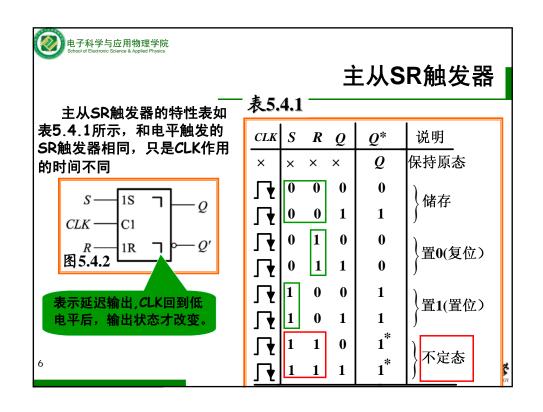

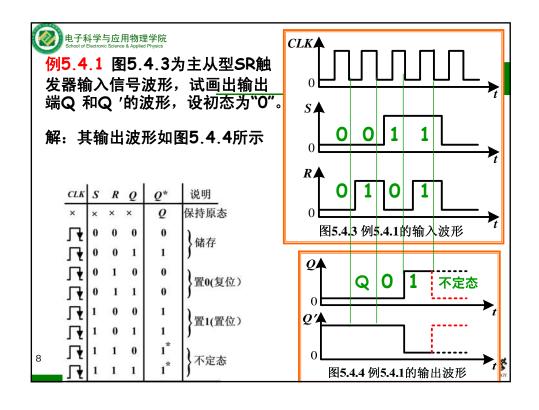

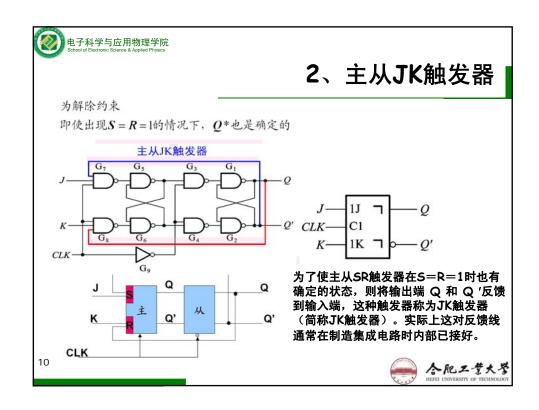

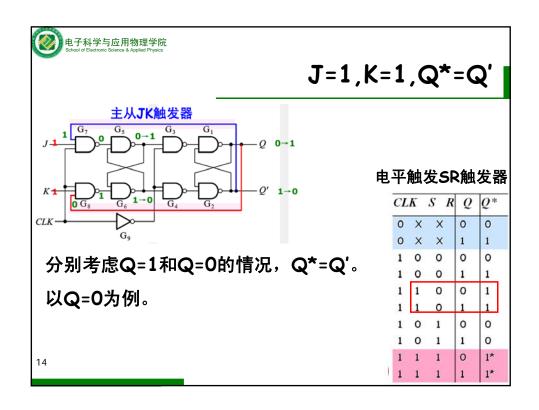

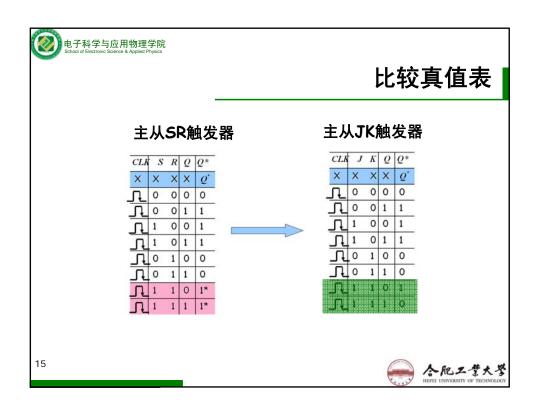

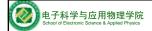

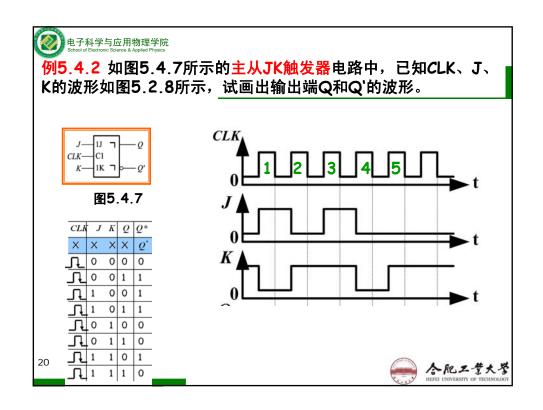

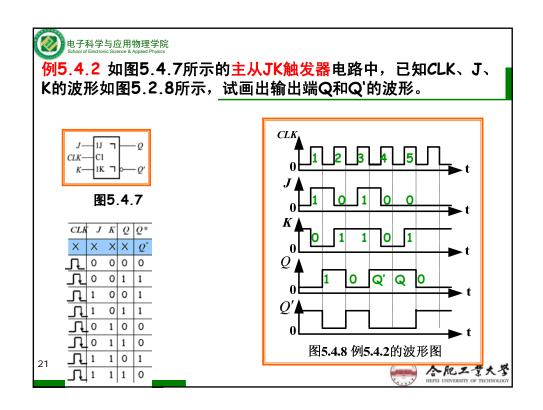

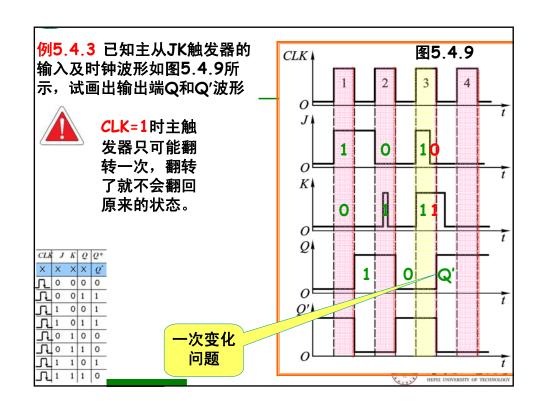

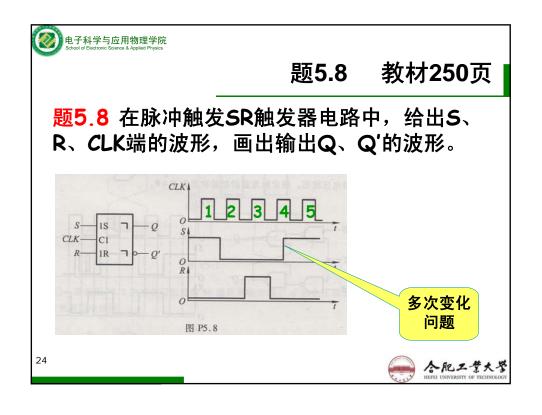

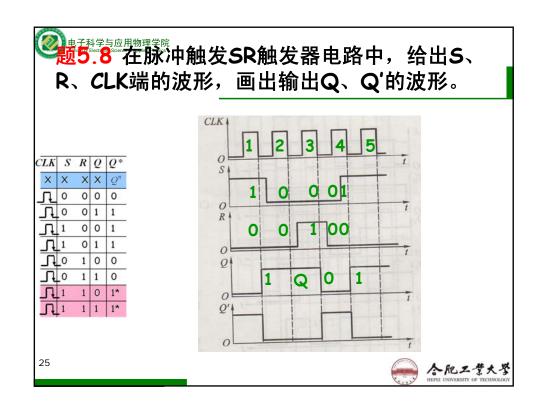

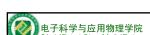

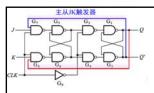

## 5.4 脉冲触发的触发器

为了避免空翻现象,提高触发器工作的可靠性,希望在每个CLK期间输出端的状态只改变一次,则在电平触发触发器的基础上设计出脉冲触发触发器。

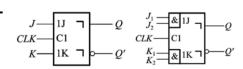

主从SR触发器(Master-Slave SR Flip-Flop)

今肥工学大学 HEFEI UNIVERSITY OF TECHNOLOGY

#### 主从RS触发器的潜在问题

注: 主从RS触发器克服了同步RS触发器在 CP=1期间多次翻转的问题,但在CLK=1 期间,主触发器的输出仍会随输入的变化 而变化,且仍存在不定态,输入信号仍遵 守SR=0。

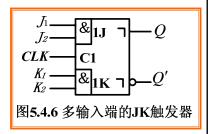

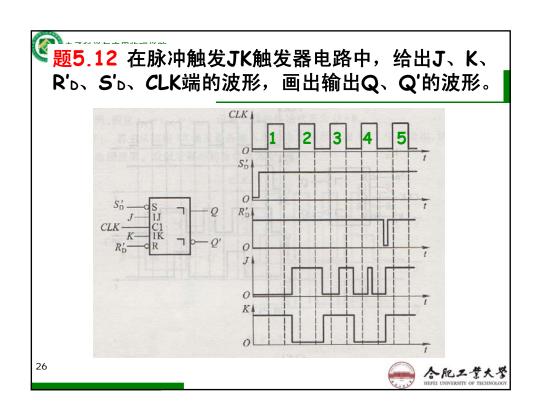

注:在有些集成触发器中,输入端J和K不止一个,这些输入端是与的关系。如图5.4.6 为其逻辑符号图。

17

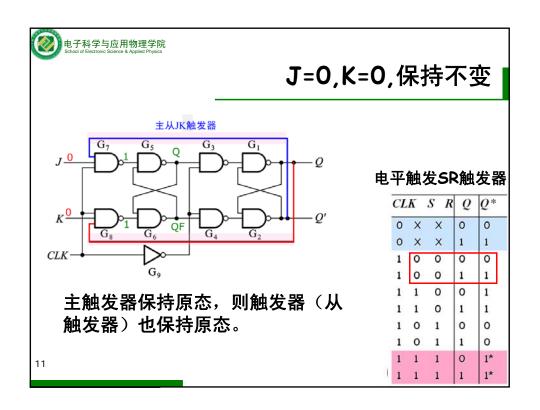

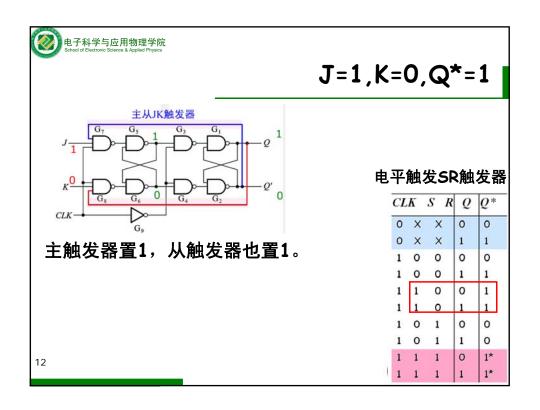

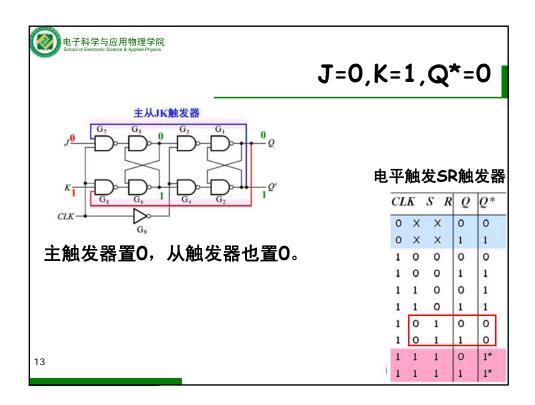

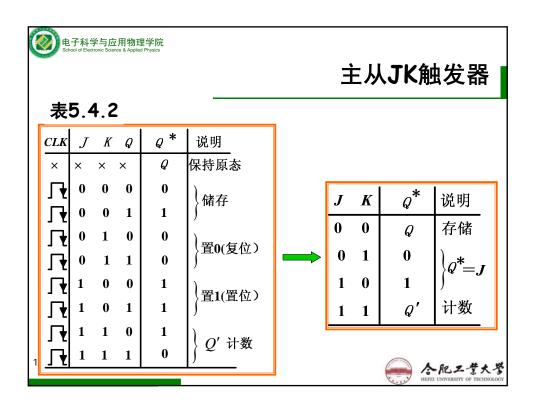

#### 二、脉冲触发方式的动作特点

- 1.分两步动作:第一步在CLK=1时,主触发器受输入信号控制,从触发器保持原态;第二步在CLK↓到达后,从触发器按主触发器状态翻转,故触发器输出状态只能改变一次;

- 2.主从JK触发器在CLK=1期间,主触发器只可能翻转一次,因为收到反馈回来的输出端的影响,故在CLK=1期间若输入发生变化时,要找出CLK ↓来到前的Q 状态,决定Q\*。

- Q=0时,只允许J=1的信号进入主触发器 Q=1时,只允许K=1的信号进入主触发器

#### 使用主从结构的注意事项

- □CLK=1 的全部时间里,输入状态始终未变的情况下,用CLK下降沿到达时输入的状态决定触发器的次态才是正确的

- □可以结合课后习题的实例来讲解。

- 5.1 概述

- 5.2 SR锁存器

- 5.3 电平触发的触发器

- 5.4 脉冲触发的触发器

- 5.5 边沿触发的触发器

- 5.6 触发器的逻辑功能及其描述方法

- \*5.7 触发器的动态特性

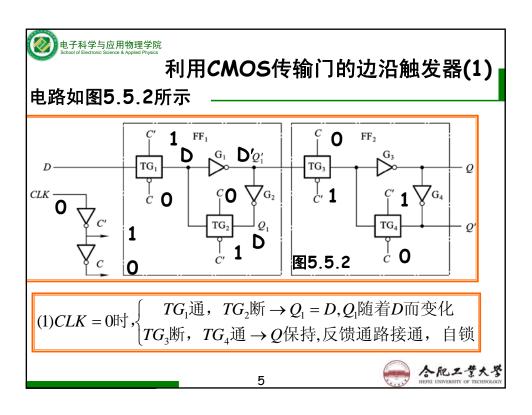

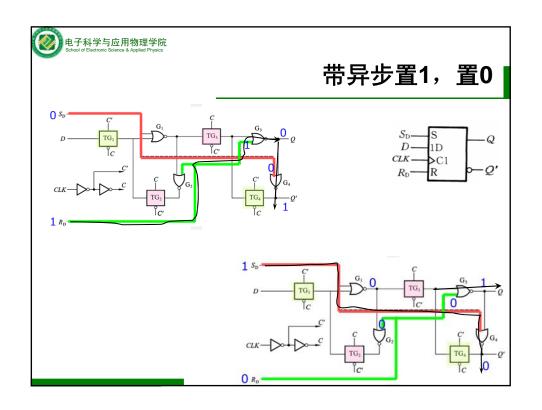

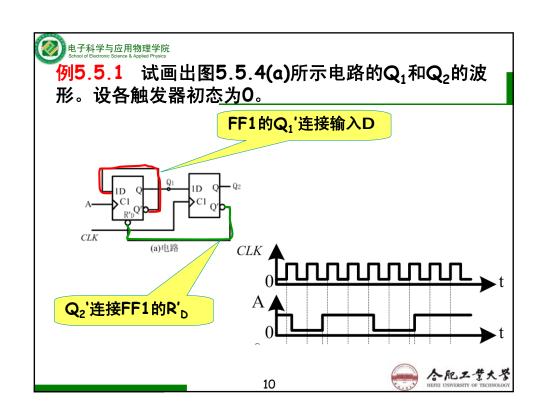

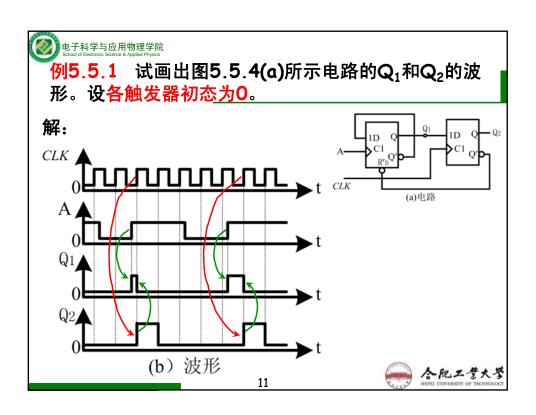

#### 5.5 边沿触发的触发器

- □ 为了提高可靠性,增强抗干扰能力,希望触发器的次态仅取决于CLK的下降沿(或上升沿)到来时的输入信号状态,与在此前、此后输入的状态没有关系

- 1. 用两个电平触发D触发器组成的边沿触发器。

- 2. 维持-阻塞触发器(略)

- 3. 利用门电路传输延迟时间的边沿触发器(略)

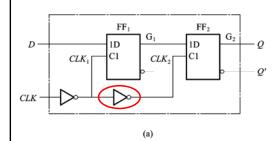

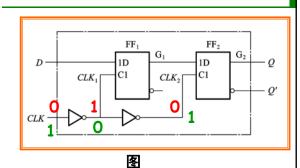

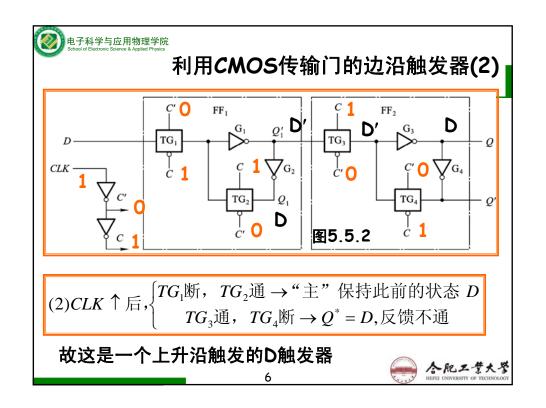

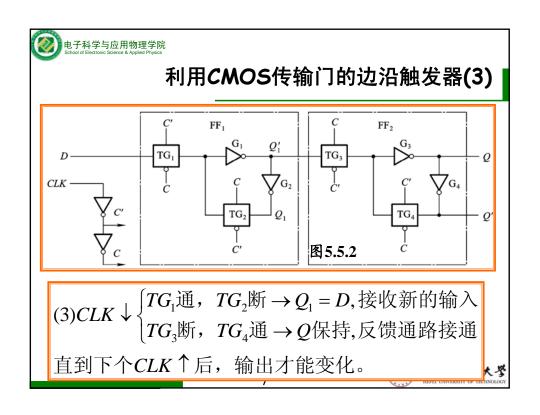

#### 1、两个电平触发D触发器组成的边沿触发器

电路如图5.5.1所示,其中  $FF_1$ 和 $FF_2$ 都是电平触发的D 触发器,它们之间也是通过 时钟相连。

3

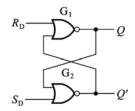

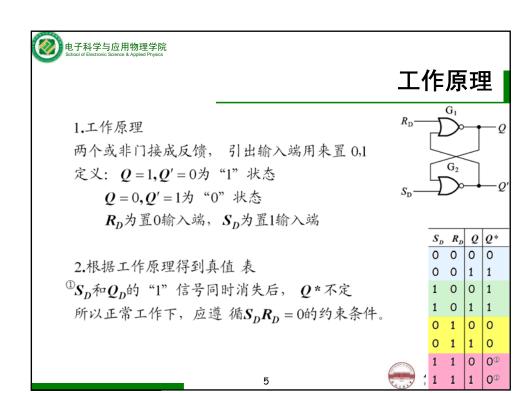

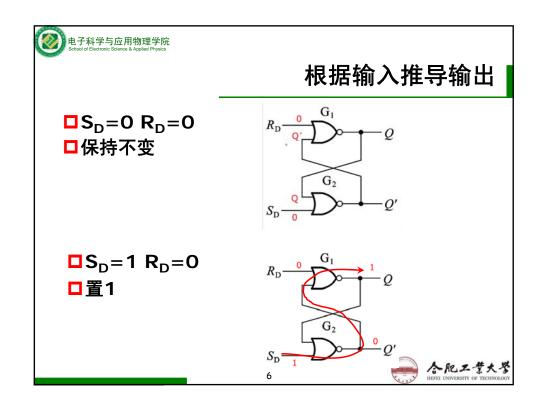

## 工作原理

#### 工作原理:

①当*CLK*=0,触发 器状态不变,FF<sub>1</sub>输 出状态与D相同;

5.5.1

②当CLK=1,即  $\int$ ,触发器 $FF_1$ 状态与前沿到来之前的 D状态相同并保持(因为 $CLK_1=0$ )。而与此同时, $FF_2$ 输出Q的状态被置成前沿到来之前的D的状态,而与其它时刻D的状态无关。

↑ REZ 学大学 HEFEI UNIVERSITY OF TECHNOLOGY

## 边沿触发器的动作特点

- □Q\*变化发生在CLK的上升沿(或者下降沿)

- □Q\*仅取决于上升沿到达时输入的状态,而 与此前、后的状态无关

- □注: Q\*是次态 (Next State)

- 5.1 概述

- 5.2 SR锁存器

- 5.3 电平触发的触发器

- 5.4 脉冲触发的触发器

- 5.5 边沿触发的触发器

- 5.6 触发器的逻辑功能及其描述方法

- \*5.7 触发器的动态特性

## 5.6 触发器的逻辑功能及其描述方法

#### 5.6.1 触发器按逻辑功能的分类

时钟控制的触发器中,由于<mark>输入方式不同</mark>(单端,双端输入)、<mark>次态随输入变化的规则</mark>不同。 分为:

- 1. SR触发器

- 2. JK触发器

- 3. T触发器

- 4. D触发器

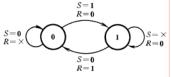

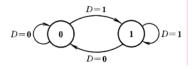

# 1、SR触发器(2)

#### 1.特性表

| S | R | Q | Q * |

|---|---|---|-----|

| 0 | 0 | 0 | 0   |

| 0 | 0 | 1 | 1   |

| 1 | 0 | 0 | 1   |

| 1 | 0 | 1 | 1   |

| 0 | 1 | 0 | 0   |

| 0 | 1 | 1 | 0   |

| 1 | 1 | 0 | 1*  |

| 1 | 1 | 1 | 1*  |

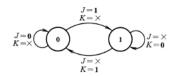

#### 3.状态转移图

4.符号

2.特性方程

$$\begin{cases}

Q^* = S'R'Q + SR'Q' + SR'Q = S'R'Q + SR' = S + R'Q \\

SR = 0

\end{cases}$$

合肥工学大学 HEFEI UNIVERSITY OF TECHNOLOGY

> 合肥工学大学 HEFEI UNIVERSITY OF TECHNOLOGY

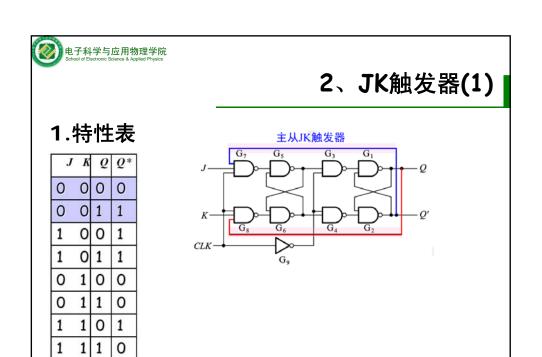

# 2、JK触发器(2)

- 1.特性表

- 2.特性方程

| 0* | = | JQ' | + | K  | 0            |

|----|---|-----|---|----|--------------|

| Y  | _ | JŲ  | Т | 11 | $\mathbf{v}$ |

- 000 0 1 1 0 0 1 0 1 0 0 0 1 1 0 1 0 1 1 1 0

- 3.状态转移图

4.符号

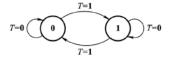

# 3. T触发器

- 1.特性表

2.特性方程

$$Q^* = TQ' + T'Q$$

- Q Q\* 0 0 0 0 1 0

- 3.状态转移图

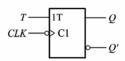

4.符号

## 4、D触发器

1.特性表

2.特性方程  $Q^* = D$

| D | Q | $Q^*$ |

|---|---|-------|

| 0 | 0 | 0     |

| 0 | 1 | 0     |

| 1 | 0 | 1     |

| 1 | 1 | 1     |

3.状态转移图

4.符号

## ⚠ 触发器之间的相互转换

□JK→SR: J、K端当作S、R端使用

□JK→T: J、K端连接在一起当作T端

□JK→D: J=K', J、K端反向连接在一起

□SR→D: S、R端反向连接在一起当作D端

□D→T: 将Q'端连接D端

✓ 重要考点

✓ 题型:选择题、填空题

合肥工学大学 HEFEI UNIVERSITY OF TECHNOLOGY

#### 5.6.2 触发器的电路结构、逻辑功能、触发方式

- □ 电路结构和逻辑功能没有——对应关系

- □SR触发器有"与非"门和"或非" 门形式

- □JK触发器也可以完成T触发器的功能

- □触发方式是由电路结构决定

- □逻辑功能和触发方式是最重要的2个属性

- ✓ 重要考点

- ✓ 题型: 选择题、判断题

11

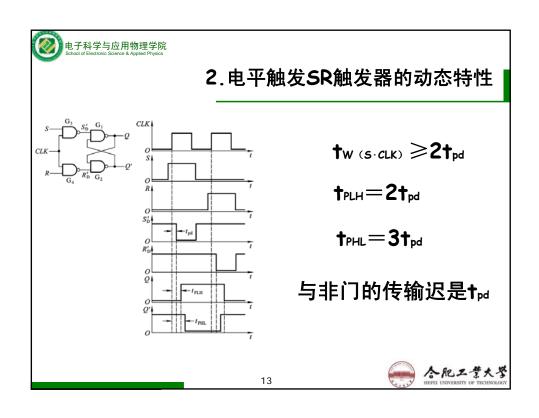

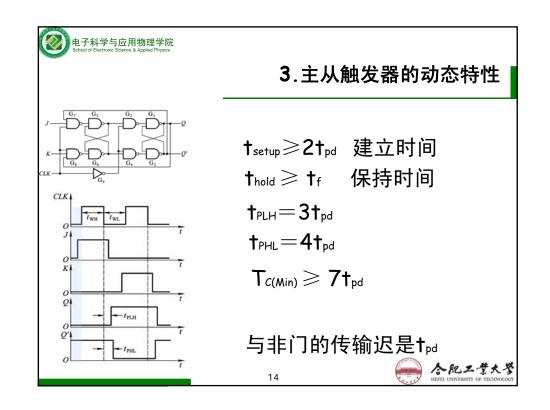

### 5.7 触发器的动态特性(略)

#### 1.SR锁存器的动态特性

$$t_W \geqslant 2t_{pd}$$

与非门的传输延迟是+品